### **Dissertation for the Degree of Doctor of Philosophy**

# **Transformer-Based RF Power Amplifiers and Signal Generations in Silicon**

**Advisor: Professor Jung-Dong Park**

Van-Son Trinh

Department of Electrical and Electronic Engineering Graduate School Dongguk University 2022

### **Dissertation for the Degree of Doctor of Philosophy**

# Transformer-Based RF Power Amplifiers and Signal Generations in Silicon

by

Van-Son Trinh

### Advisor: Professor Jung-Dong Park

. 2022/07

|                  | Date of submission : 2022/06<br>Date of approval : 2022/07 |               |

|------------------|------------------------------------------------------------|---------------|

| Approved by:     |                                                            | $\Lambda$ .   |

| Chairman         | : Professor Han Ho Choi                                    | Sign          |

| Committee member | : Professor Nam-Seog Kim                                   | ABignan       |

| Committee member | : Professor Jae-Duk Han                                    | Sign          |

| Committee member | : Professor Min-Sung Kim                                   | Asimensing in |

| Committee member | : Professor Jung-Dong Park                                 | (Sign)        |

Department of Electrical and Electronic Engineering Graduate School Dongguk University 2022

\*

#### ACKNOWLEDGMENTS

In the first place, I would like to express my profound gratitude to Professor Park Jung-Dong for his numerous encouragements, guidance, and support during my study and life at Dongguk University. Throughout the highs and lows of my Ph.D. journey, he has always been generous, attentive, available, and encouraging. Thanks to his extensive experience and firm and solid knowledge, I have learned the principles of RF integrated circuit design and gained valuable academic experience.

Also, I would like to thank all the committee members for their prudent and valuable guidance during my doctoral dissertation. It has been very helpful to have their constructive suggestions and opinions.

Taking this opportunity, I would like to thank all the people I have met and worked with at MEIC Lab. at Dongguk University, Dr. Don-Hwa Lee, Dr. Hyo-Hyun Nam, Jeong-Moon, Van-Viet, Young Joe, Hsiang-Nerng Chen, Tae-Wha, Hyeon-Seok, Jun-Hee, Van-Du, Hyeon-Hee, and Hyeong-Geun. I have taken a lot of technical help and instruction from my senior Hyo-Hyun. It is also a good chance to enrich knowledge and experience when working with other members. As an international student, it could be lonelier and more difficult for me to settle the life without the friendly help and the shares from other members and Vietnamese friends.

Most importantly, I wish to acknowledge and thank my family and my wife, Nguyen Thi Trang, for their endless support and love. It would not be possible for me to achieve what I have without their dedication and sacrifice.

#### ABSTRACT

The last decade has witnessed a rapid growth of RF transceivers in various applications such as broadband wireless links for the 4<sup>th</sup> and 5<sup>th</sup> generations of communication, medical imaging, radar, and spectroscopy. Various performance merits are required for a transceiver platform specification, such as bandwidth, gain, linearity, efficiency, noise resistance, area occupancy, and power consumption. Modern transceiver design has faced challenges of deficiency in the output power with low efficiency for signal transmission due to the adverse effect of the scaling down of the MOS-transistor channel length to attain higher speed and lower power consumption in digital blocks. Moreover, the movement toward higher operating frequencies also degrades the intrinsic gain of active devices (i.e., MOSFET or BJT) and increases the loss of passive components (capacitors, inductors, transformers, and power combiners/splitters).

This dissertation deals with improving the power amplification and signal generation for RF transceivers in silicon. The first research topic focuses on enhancing efficiency and output power for power amplifiers in the various microwave and millimeter-wave regimes. The second topic deals with improving the harmonic rejection ratio in the frequency multiplier which is an essential building block in high-quality signal generation in the millimeter-wave regime. Regarding power amplification, we perform a detailed analysis of the impedance matching for push-pull amplifiers using a transformer-based matching circuit which is among the most frequently employed structure in CMOS power amplifier (PA) design. The reliability of the push-pull amplifiers has also been analyzed using network theory to ensure its stable operation when implementing matching components and biasing circuits to prevent common-mode oscillation. Several PAs designed with the established principles have been successfully demonstrated in X-band, E-band, and sub-terahertz (sub-THz) regions. To enhance the output power of the CMOS PAs, we have introduced a transformer-based novel power combiner operating with current and voltage modes at the X-band to boost the output power by higher than 25-dBm while achieving a power-added efficiency of 25-% in 65-nm CMOS. An

efficient power combining in the voltage domain at higher frequencies becomes more challenging due to the low self-resonant frequency (SRF) from the relatively lengthy routing structure of the transformer-based combiners at the millimeter-wave regime. To overcome this issue from the transformer-based power combining structure at high frequency, we have explored the potential usefulness of the high-way power combining architecture in the voltage mode and successfully demonstrated an Eband eight-way CMOS power amplifier in 65nm CMOS technology. The fabricated PA achieved up to 19-dBm of output power at 85-GHz which was the first E-band PA operating beyond the SRF of the transformer-based power combiner to date. As a core building block of the high-performance local oscillator (LO), frequency multipliers have been increasingly utilized in millimeter-wave LO blocks considering their wide tuning range and low phase noise performance. To further improve the harmonic rejection of the transformer-based push-pull doubler, we have introduced imbalanced capacitive loads to compensate for intrinsic impedance imbalance at the differential terminals of the transformers. The proposed methodology was applied an eight-time frequency multiplier operating at E-band in 65nm CMOS, and the porotype demonstrated more than 10 times of improvement in the harmonic rejection compared with that without the imbalanced capacitive loads.

## **TABLE OF CONTENTS**

| ABSTRACT                                                              | i    |

|-----------------------------------------------------------------------|------|

| LIST OF FIGURES                                                       | v    |

| LIST OF TABLES                                                        | ix   |

| ABBREVIATIONS                                                         | X    |

| I. Introduction                                                       | 1    |

| 1.1. Motivation                                                       | 1    |

| 1.2. Applications                                                     | 3    |

| 1.2.1. Active Electronically Scanned Array (AESA) in X-band           | 3    |

| 1.2.2 Automotive radar at 77-GHz                                      | 4    |

| 1.2.3 Point-to-point wireless communication in E-band for 5G backhaul | 6    |

| 1.2.4 Wireless communication at the sub-terahertz band                | 7    |

| 1.3. Thesis organization                                              |      |

| 1.4. Reference                                                        | 9    |

| II. Impedance matching and stability analysis for TF-based PA         | . 11 |

| 2.1 Introduction                                                      | . 11 |

| 2.2 Impedance matching for transformers                               | . 12 |

| 2.3 Common-mode instability in push-push power amplifiers             |      |

| 2.3.1 Introduction                                                    | . 17 |

| 2.3.2 Oscillation mechanism in differential amplifiers                | . 18 |

| 2.3.3 Stabilization methods for differential amplifiers               | . 22 |

| 2.4 Reference                                                         |      |

| III. X-band transformer-coupled power amplifiers                      | . 31 |

| 3.1 Introduction                                                      | . 31 |

| 3.2 Power amplifier design using voltage and current power combining  |      |

| 3.2.1 Architecture consideration                                      |      |

| 3.2.2 Stabilizing push-pull amplifiers                                |      |

| 3.2.3 Gate bias voltage consideration                                 |      |

| 3.2.4 Device sizing and impedance matching                            | . 39 |

| 3.2.5 Measurement results                                             | . 42 |

| 3.3 Power amplifier design using 1:2 output transformer               | . 45 |

| 3.3.1 Power amplifier design                                          | . 45 |

| 3.3.2 Measurement results                                             | . 49 |

| 3.4 Single-pull class A/B power amplifier design                      | . 51 |

| 3.4.1 Design the Two-Stage Single-Pull Power Amplifier                | . 51 |

| 3.4.2 Measurement results                                             | . 53 |

| 3.5 Reference                                                         |      |

| IV. E-band Transformer-coupled Power Amplifiers                       | . 58 |

| 4.1 Introduction                                                  |                |

|-------------------------------------------------------------------|----------------|

| 4.2 Compact and high-efficiency power amplifier design in 77-GHz  | 60             |

| 4.2.1 Power amplifier design                                      | 61             |

| 4.2.2 Measurement results                                         | 67             |

| 4.3 Power amplifier design using power combiner beyond the SRF.   | 70             |

| 4.3.1 Operation of power combiner beyond the SRF                  | 70             |

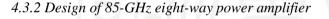

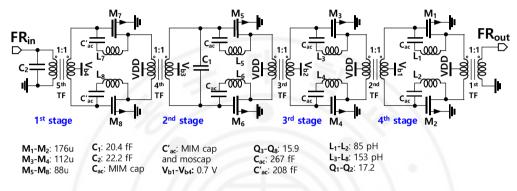

| 4.3.2 Design of 85-GHz eight-way power amplifier                  | 75             |

| 4.3.3 Measurement results                                         | 83             |

| 4.4 Push-pull power amplifier design using inductive feedback     |                |

| 4.4.1 Power amplifier design                                      | 86             |

| 4.4.2 Measurement results                                         | 89             |

| 4.5 Reference                                                     | 91             |

| V. Signal Generation in E-band                                    |                |

| 5.1 Introduction                                                  |                |

| 5.2 Design of an eight-time E-band frequency multiplier           | 96             |

| 5.2.1 Transformer-based balun design using balancing capacitors   |                |

| 5.2.2 Eight-time frequency multiplier design                      | 108            |

| 5.3 Measurement results                                           | 114            |

| 5.4 Reference                                                     | 117            |

| VI. A Sub-THz Amplifier                                           | 120            |

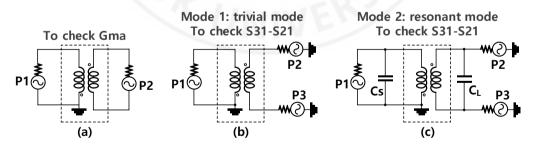

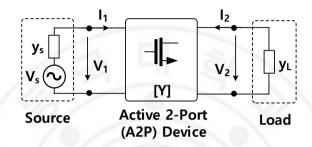

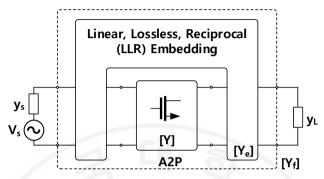

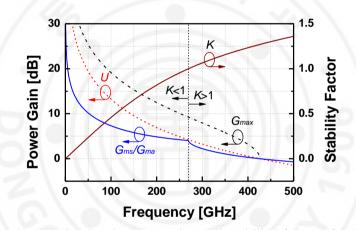

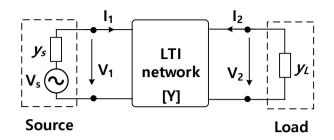

| 6.1 Gain of transistor and impedance matching for a two-port netw | <b>ork</b> 120 |

| 6.2. A design of 280-GHz amplifier in SiGe                        | 124            |

| 6.3 A design of 280-GHz receiver in SiGe                          |                |

| 6.4. Reference                                                    |                |

| APPENDIX A                                                        | 132            |

|                                                                   |                |

|                                                                   |                |

|                                                                   |                |

|                                                                   |                |

### LIST OF FIGURES

| Figure 1.1. Typical simplified RF interface of a transceiver system                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2. Applications of power amplifiers over frequency bands [1.4]                                                                        |

| Figure 1.3. Simplified block diagram of AESA system                                                                                            |

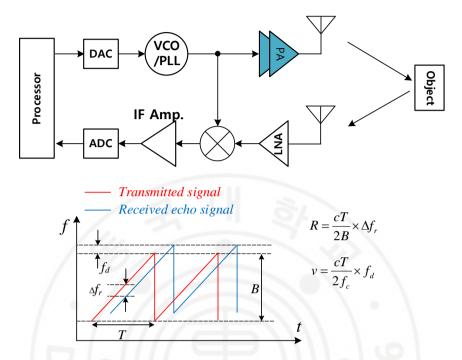

| Figure 1.4. Simplified block diagram and working principle of an FMCW radar                                                                    |

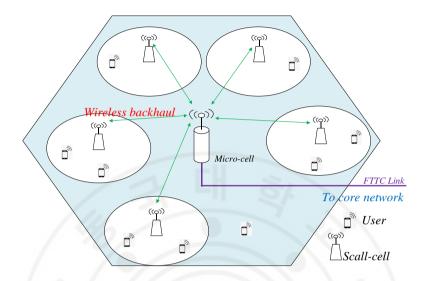

| Figure 1.5. The logical architecture of the 5G backhaul network [1.11]                                                                         |

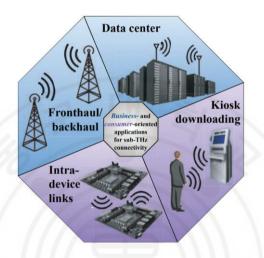

| Figure 1.6. Target applications of wireless communication at sub-THz bands [1.17]7                                                             |

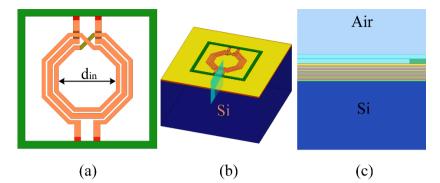

| Figure 2.1. On-chip 2:1 TF structure for 3D electromagnetic simulation: (a) the front face,                                                    |

| (b) a 3D view in HFSS, and (c) a side view of the layer stacks                                                                                 |

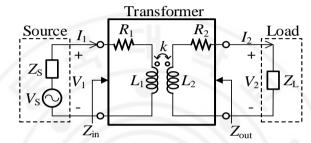

| Figure 2.2. Magnetically coupled TF model with load and source                                                                                 |

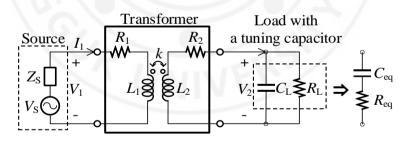

| Figure 2.3. The TF impedance matching network using a parallel capacitor14                                                                     |

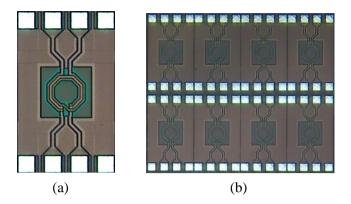

| Figure 2.4. Photographs of the on-chip TFs in 0.18 µm CMOS: (a) the standalone 2:1                                                             |

| transformer, and (b) transformers with parallel tuning capacitors15                                                                            |

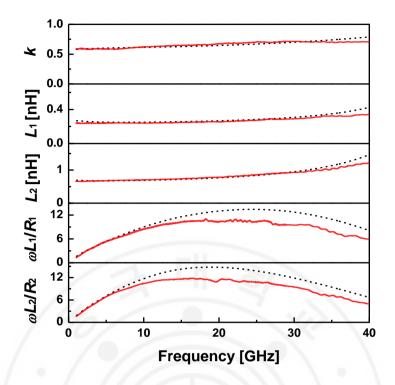

| Figure 2.5. Effective parameters of the on-chip 2:1 TF on simulation (dashed line) and                                                         |

| measurement (solid line)                                                                                                                       |

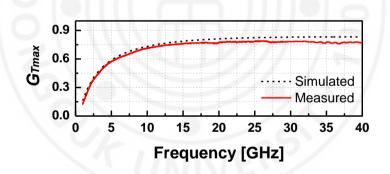

| Figure 2.6. G <sub>Tmax</sub> versus frequency of the on-chip 2:1 TF16                                                                         |

| Figure 2.7. Power efficiency versus parallel tuning capacitances for the on-chip 2:1 TF at 10                                                  |

| GHz17                                                                                                                                          |

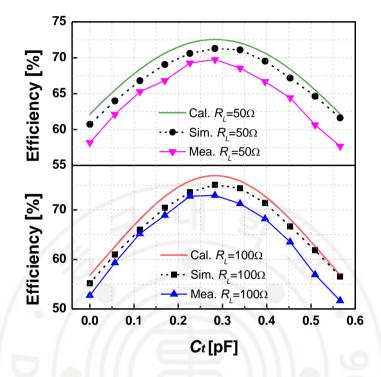

| Figure 2.8. Instability in differential amplifiers (a) A pseudo-differential amplifier, (b) a                                                  |

| push-pull amplifier, and (c) the simulated oscillation of the drain voltage of a transistor in a                                               |

| push-pull structure after turning on the supply voltage when there is no input signal 19                                                       |

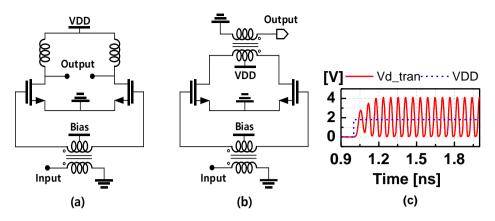

| Figure 2.9. Common-mode equivalent circuit of push-pull amplifiers (a) a schematic of the                                                      |

| push-pull amplifier, (b) the small-signal common-mode half-circuit of the PA, and (c) a                                                        |

| simplified version of the circuit in (b)                                                                                                       |

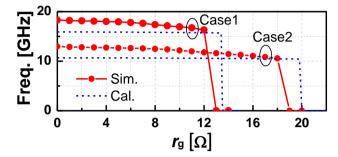

| Figure 2.10. Calculated and simulated oscillation frequencies versus $R_g$ : Case 1: $L_g=L_d$                                                 |

| =250 pH and Case 2: Lg=Ld=500 pH23                                                                                                             |

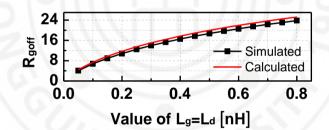

| Figure 2.11. Calculated and simulated gate resistances which prohibited the unstable                                                           |

| oscillations ( $R_d = (2\pi \times 10G \times L_d)/10$ )                                                                                       |

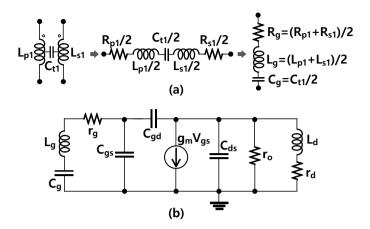

| Figure 2.12. Effect of the coupling capacitance between the coils of the TF (a) the parasitic                                                  |

| capacitance between the two coils of the input transformer and (b) the small-signal CM                                                         |

| half-circuit of the PA24                                                                                                                       |

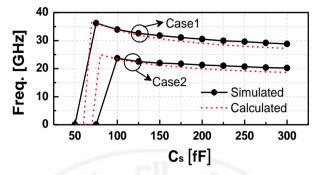

| Figure 2.13. The calculated and simulated oscillation frequencies versus $C_g$ : Case 1:                                                       |

| $L_g\!\!=\!\!300 \text{ pH}, L_d\!\!=\!\!200 \text{ pH} \text{ and } \textbf{Case 2:} L_g\!\!=\!\!600 \text{ pH}, L_d\!\!=\!\!400 \text{ pH}.$ |

| Figure 2.14. A schematic of the common-mode half-circuit push-pull amplifier with an RC                                                        |

| feedback circuit (the bias circuit is hidden)                                                                                                  |

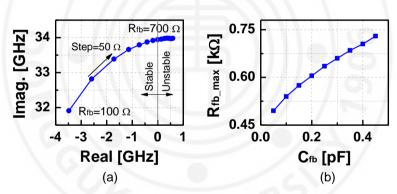

| Figure 2.15. (a) The root locus of the point causes instability versus the value of $R_{\rm fb}.$ (b) The                                      |

| simulated maximum value of $R_{\rm fb}$ is required to turn off oscillation                                                                    |

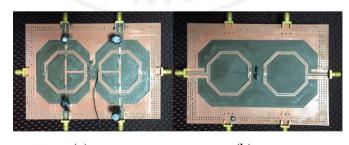

| Figure 2.16. The on-board push-pull amplifier. (a) the front side and (b) the backside 27                                                      |

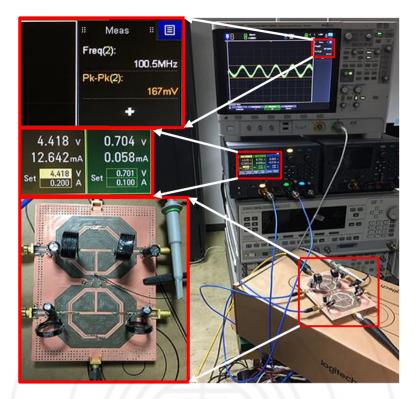

| Figure 2.17. Measurement of common-mode oscillation in the push-pull amplifier                                                                 |

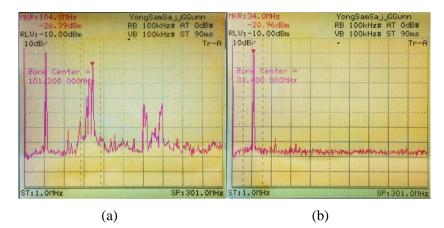

| Figure 2.18. Output spectrum before stabilization (a) and after stabilization by using a 50 $\Omega$                                           |

| resister at the base bias line (b)                                                                                                             |

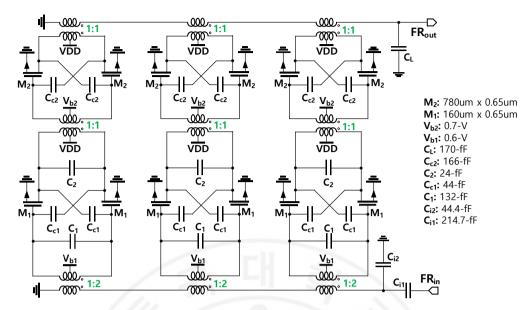

| Figure 3.1. Complete schematic of the X-band CMOS two-stage PA using six-way voltage                                |

|---------------------------------------------------------------------------------------------------------------------|

| power combining/splitting architecture                                                                              |

| Figure 3.2. Conventional TF-based voltage combiners (a) and current combiners (b) 34                                |

| Figure 3.3 HFSS implementations of the power combiner (a) and power splitter (b)                                    |

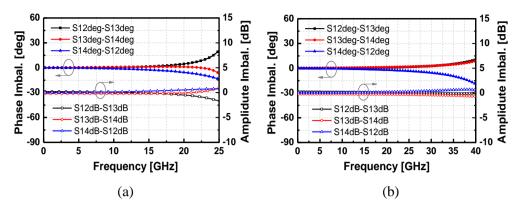

| Figure 3.4. Simulated phase/amplitude imbalances of the (a) output 3-way power combiner                             |

| and (b) input 3-way power splitter                                                                                  |

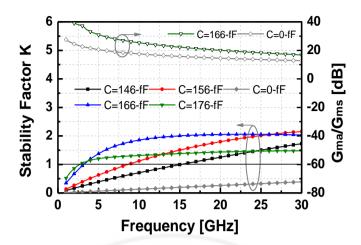

| Figure 3.5. Simulated G <sub>ms</sub> /G <sub>ma</sub> and stability factor K versus frequency of several values of |

| the neutralization capacitor (C <sub>neu</sub> )                                                                    |

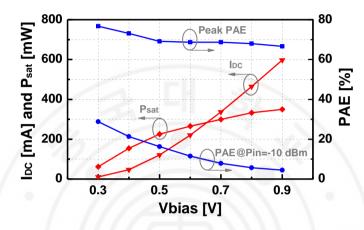

| Figure 3.6. Simulated peak PAE, PAE at P <sub>in</sub> =-10-dBm, saturated output power (P <sub>sat</sub> ), and    |

| DC current consumption $(I_{DC})$ of the output transistor differential amplifier versus the gate                   |

| bias voltage (V <sub>bias</sub> )                                                                                   |

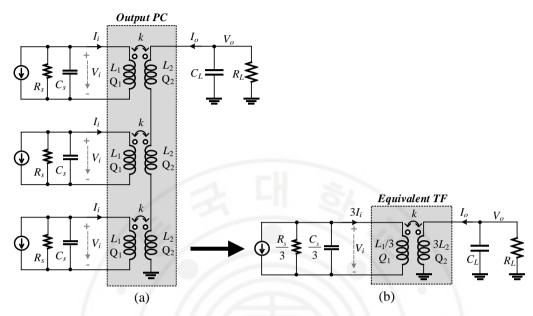

| Figure 3.7. Schematic (a) and the equivalent TF model (b) of the output stage40                                     |

| Figure 3.8. 3D HFSS physical structure of the whole PA                                                              |

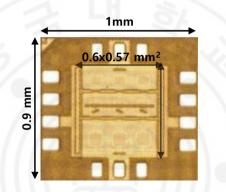

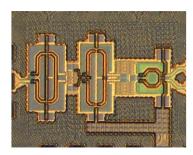

| Figure 3.9. Photograph of the fully integrated X-band 6-way power combining PA chip42                               |

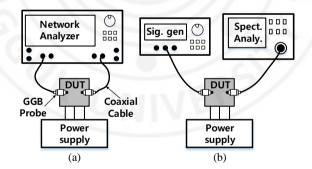

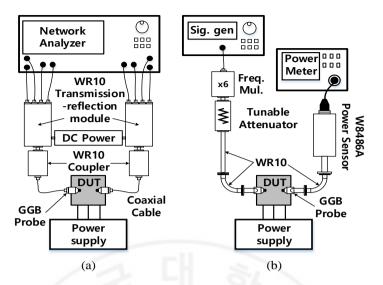

| Figure 3.10. Measurement setups of the S-parameters (a) and large-signal merits (b)42                               |

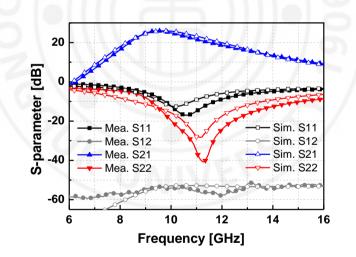

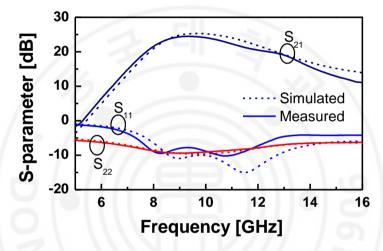

| Figure 3.11. Simulated and measured S-parameters of the 6-way PA                                                    |

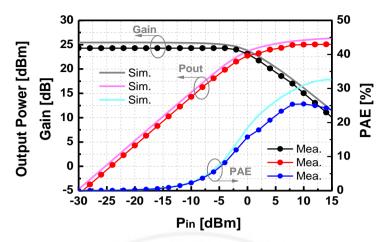

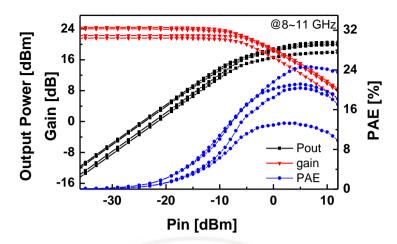

| Figure 3.12. Simulated and measured output power (Pout), Gain, and power-added efficiency                           |

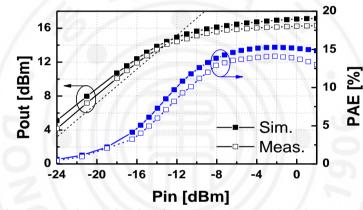

| (PAE) versus input power (Pin) of the PA at 10-GHz                                                                  |

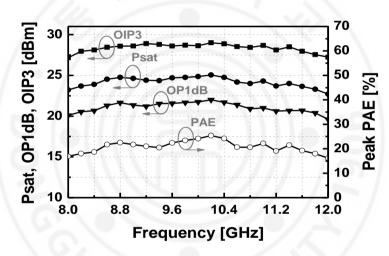

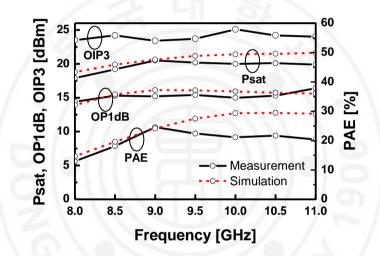

| Figure 3.13. Measured Psat, OP1dB, OIP3, and peak PAE of the 6-way PA in the X-                                     |

| band                                                                                                                |

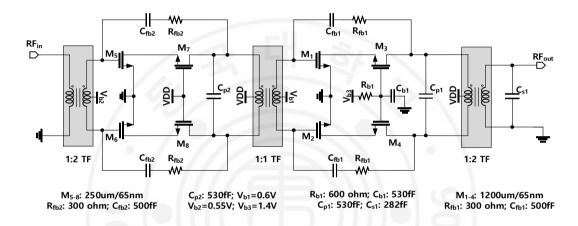

| Figure 3.14. A schematic of the two-stage TF-coupled PA                                                             |

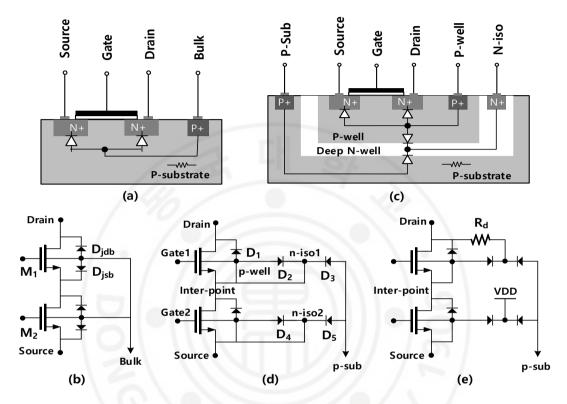

| Figure 3.15. Cascade structure of NMOS (a) The structure of the bulk CMOS, (b) the                                  |

| schematics of the NMOS cascode with the bulk CMOS, (c) the structure of the triple-well                             |

| CMOS, (d) the schematics of the conventional cascode with the triple-well CMOS, and (e)                             |

| the triple-well CMOS cascode with the biasing resistor $(R_b)$ 47                                                   |

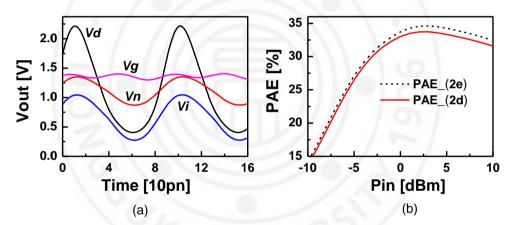

| Figure 3.16. (a) The simulated voltage waveforms of the nodes in Figure 3.15e: drain $(V_d)$ ,                      |

| n-iso1 ( $V_n$ ), gate1 ( $V_g$ ), and inter-point ( $V_i$ ). (b) The power-added efficiency of the PA              |

| when using the configurations in Figure 3.15d (PAE_{2d}) and Figure 3.15e (PAE_{2e})                                |

| Figure 3.17. A microphotograph of the CMOS PA using 1:2 output TF                                                   |

| Figure 3.18. S-parameter versus frequency of the X-band 65-nm CMOS PA                                               |

| Figure 3.19. The measured power performance of the PA in the range of 8-11 GHz in 1                                 |

| GHz increments                                                                                                      |

| Figure 3.20. The measured and simulated saturated power output (Psat), OP1dB, and peak                              |

| PAE along with measured OIP3 versus frequency50                                                                     |

| Figure 3.21. Schematic circuit of the two-stage single-pull power amplifier on 180-nm                               |

| CMOS                                                                                                                |

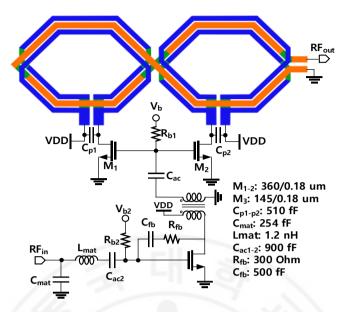

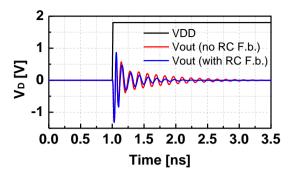

| Figure 3.22. The output waveform of the PA when the VDD is turned on at 1ns in the case                             |

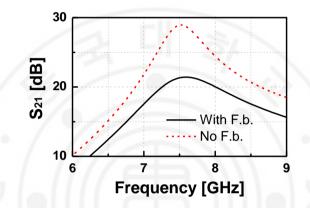

| with and without the shunt RC feedback53                                                                            |

| Figure 3.23. The gain (S21) of the PA in the case with and without the shunt RC                                     |

| feedback                                                                                                            |

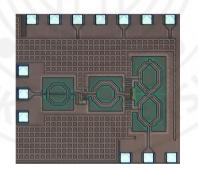

| Figure 3.24. The microphotograph of the fabricated two-stage PA on a 180-nm CMOS                                    |

| process (full chip size is 0.83mm×0.52mm)                                                                           |

| Figure 3.25. Simulated and measured S-parameters of the single-pull PA                                             | 54 |

|--------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.26.The simulated and measured power performance of the PA at 8GHz                                         | 54 |

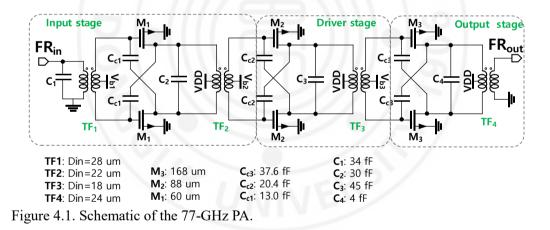

| Figure 4.1. Schematic of the 77-GHz PA.                                                                            | 61 |

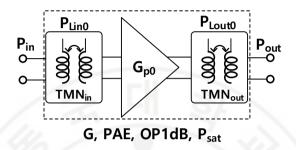

| Figure 4.2. An amplifier with input and output matching networks                                                   | 62 |

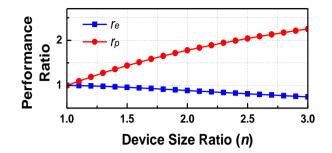

| Figure 4.3. Power gain and efficiency compression ratios (r <sub>e</sub> and r <sub>p</sub> ) versus the increased |    |

| ratio of the active device size (n)                                                                                | 64 |

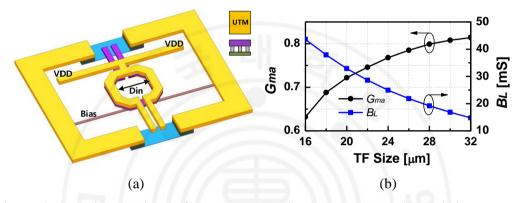

| Figure 4.4. Implemented transformer structure in 65-nm CMOS (a) and the extracted                                  |    |

| optimal load susceptance (B <sub>L</sub> ), and the maximum available gain (G <sub>ma</sub> ) of transformers wit  | h  |

| different inner diameter sizes (D <sub>in</sub> ) (b).                                                             | 64 |

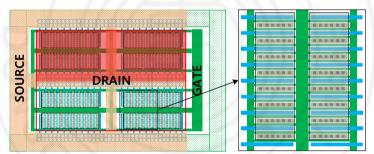

| Figure 4.5. Simplified layout of a transistor using a table structure.                                             | 65 |

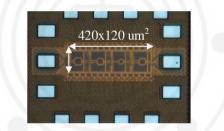

| Figure 4.6. A Photograph of the fabricated 77-GHz PA in a 65-nm CMOS                                               | 67 |

| Figure. 4.7. Measurement setup for (a) S-parameters and (b) Large-signal performances                              |    |

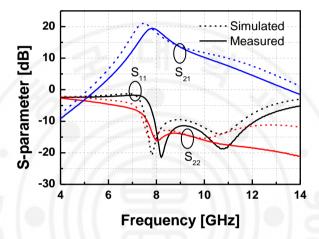

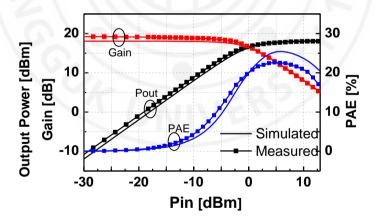

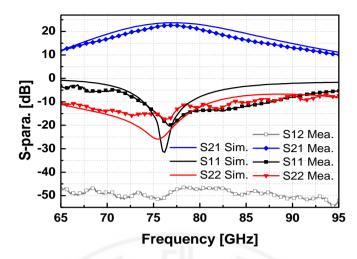

| Figure 4.8. Simulated and measured S-parameters of the 77-GHz PA.                                                  | 69 |

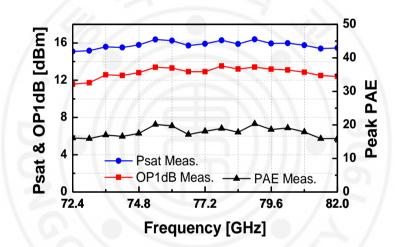

| Figure 4.9. Measured saturated output power (Psat), output 1-dB gain compression point,                            |    |

| and PAE versus frequency.                                                                                          | 69 |

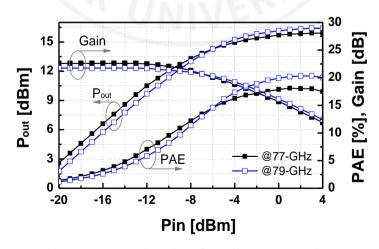

| Figure 4.10. Measured output power (Pout), gain, and PAE versus input power                                        | 69 |

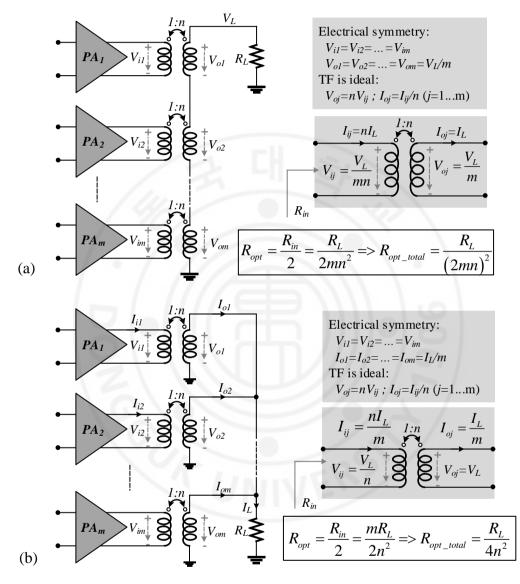

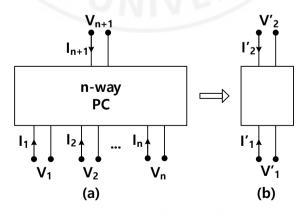

| Figure 4.11. An n-way power combiner (a) and its equivalent two-port (b) when the                                  |    |

| voltages are identical at all the input ports.                                                                     | 70 |

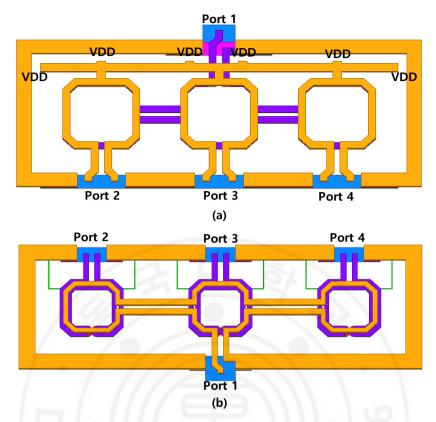

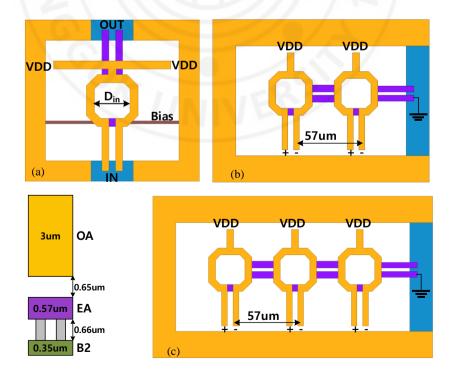

| Figure 4.12. The implementation of (a) the transformer and PCs/PSs in the voltage domain                           |    |

| (b) a 2-way PC/PS, and (c) a 3-way PC/PS in the HFSS                                                               |    |

| Figure 4.13. G <sub>ma</sub> of the D2SE 26-µm TF and the E2PNs of the two voltage PCs                             |    |

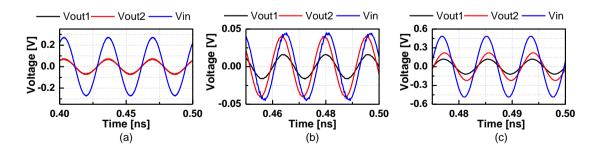

| Figure 4.14. The simulated voltage waveforms of the two output ports (Vout1 and Vout2) and                         | d  |

| the input port (Vin) of the 2-way PSV in Figure 4.11b when an input signal of 0-dBm is                             |    |

| applied: (a) $F_{in} = 30$ GHz, (b) $F_{in} = 62$ GHz, and (c) $F_{in} = 120$ GHz.                                 | 73 |

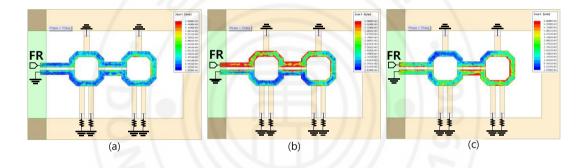

| Figure 4.15. The simulated current distribution of the 2-way PSV shown in Figure 4.12b a                           | ıt |

| different input-signal frequencies: (a) $F_{in} = 30$ GHz, (b) $F_{in} = 62$ GHz, and (c) $F_{in} = 120$           |    |

| GHz.                                                                                                               | 74 |

| Figure 4.16. A schematic of a CMOS with the proposed W-band 8-way 4-stage PA using                                 |    |

| PC/PS in both the voltage and current domains.                                                                     | 75 |

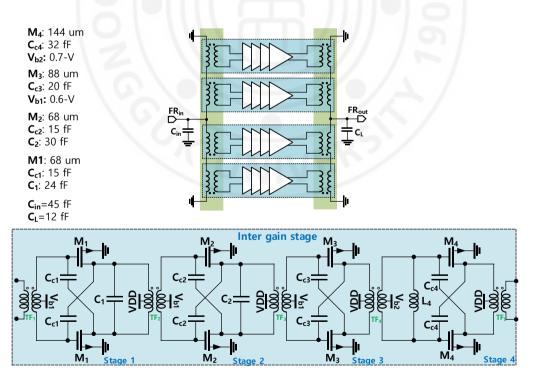

| Figure 4.17. Equivalent circuits of the output PC.                                                                 | 76 |

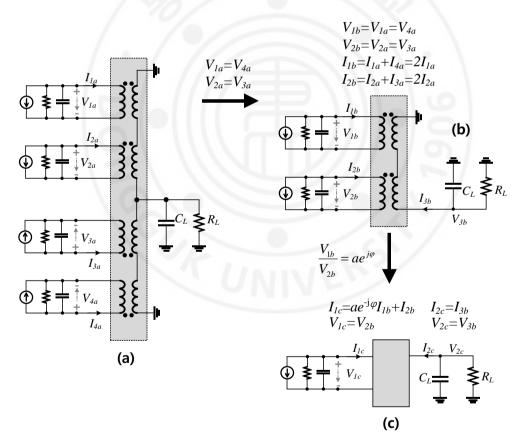

| Figure 4.18. Simulated maximum efficiency at 85 GHz of the output PC versus the                                    |    |

| amplitude ratio (a) and phase difference ( $\phi$ ) between V <sub>1b</sub> and V <sub>2b</sub>                    | 78 |

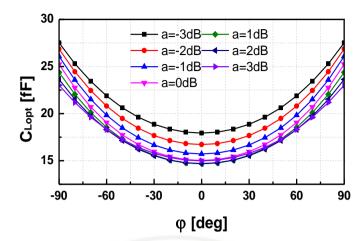

| Figure 4.19. Calculated $C_{Lopt}$ versus amplitude imbalance a, and phase imbalance $\phi$                        | 79 |

| Figure 4.20. Simulated amplitude and phase imbalance between the inside port (port 1) an                           | d  |

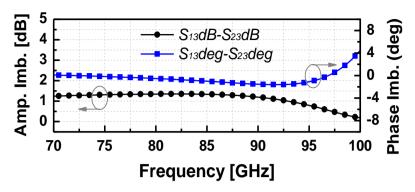

| the outside port (port 2) to the input port (port 3) in the input PS.                                              | 82 |

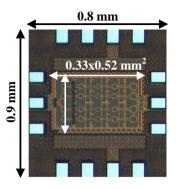

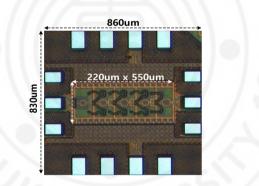

| Figure 4.21. A photograph of the fabricated 8-way PA in 65-nm CMOS                                                 | 84 |

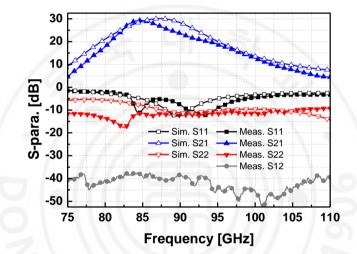

| Figure 4.22. The simulated and measured S-parameters of the proposed 8-way PA                                      | 84 |

| Figure 4.23. The measured P <sub>sat</sub> , OP1dB, and PAE of the 8-way PA.                                       | 85 |

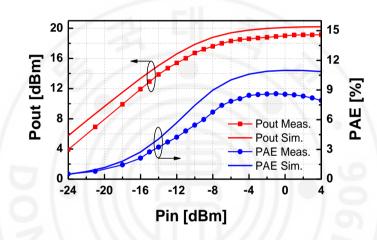

| Figure 4.24. Simulated and measured output power (Pout) and PAE of the 8-way PA                                    |    |

| according to input power (Pin) at 86.4 GHz.                                                                        | 85 |

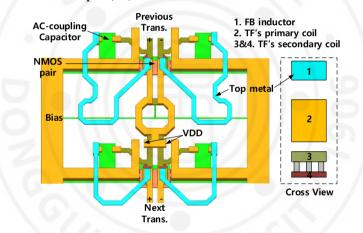

| Figure 4.25. Schematic of the inductive feedback push-pull PA                                                      | 87 |

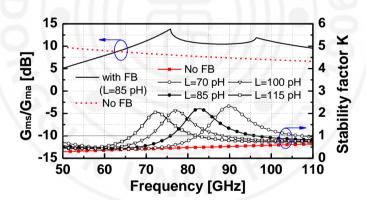

| Figure 4.26. G <sub>ms</sub> /G <sub>ma</sub> and stability factor K against frequency in several values of feedback                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| inductances                                                                                                                                   |

| Figure 4.27. The physical layout of the feedback inductor for a push-pull PA                                                                  |

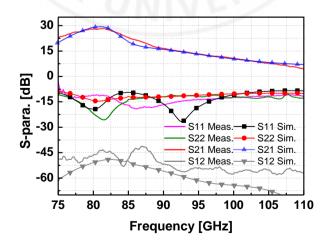

| Figure 4.29. Simulated and measured S-parameters of the PA90                                                                                  |

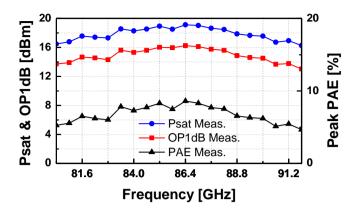

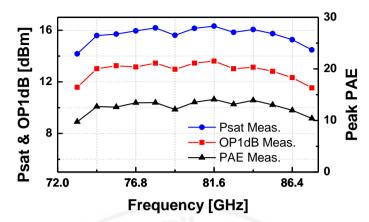

| Figure 4.30. The saturated output power (Psat), output 1-dB gain compression point                                                            |

| (OP1dB), and power-added efficiency (PAE) of the measured PA90                                                                                |

| Figure 4.31. The measured and simulated output power (Pout) and PAE versus input power                                                        |

| (P <sub>in</sub> )                                                                                                                            |

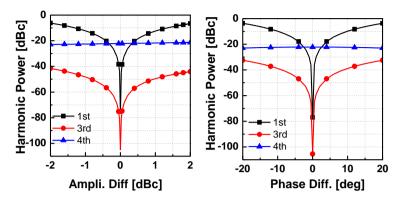

| Figure 5.1. Effect of the unbalanced input on the harmonic rejection performance                                                              |

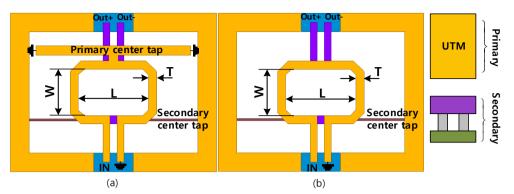

| Figure 5.2. HFSS-realization of (a) TF-based balun with AC-grounded primary center tap                                                        |

| used in the FM design and (b) a typical TF-based balun                                                                                        |

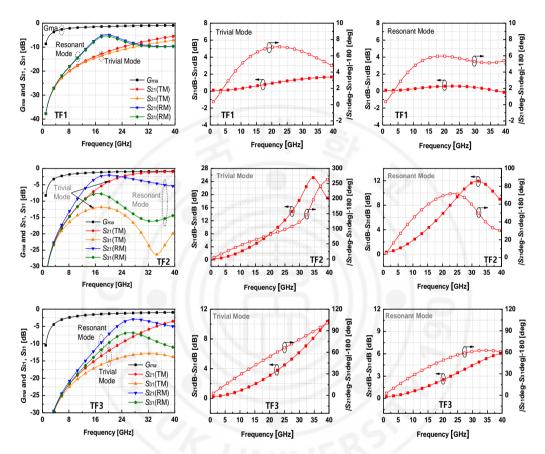

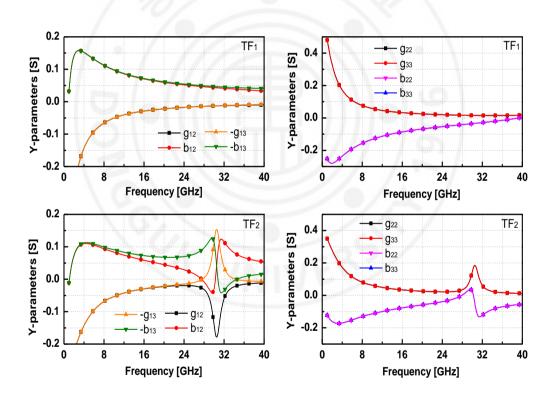

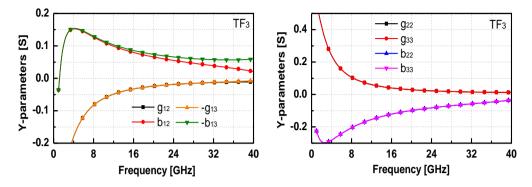

| Figure 5.4. Simulated efficiency score (G <sub>ma</sub> ) and output balance score (S21-S31) of the                                           |

| three TF-based baluns                                                                                                                         |

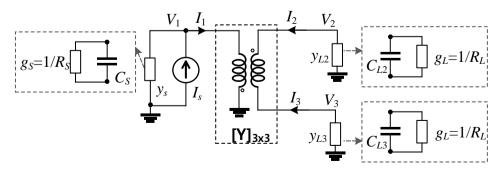

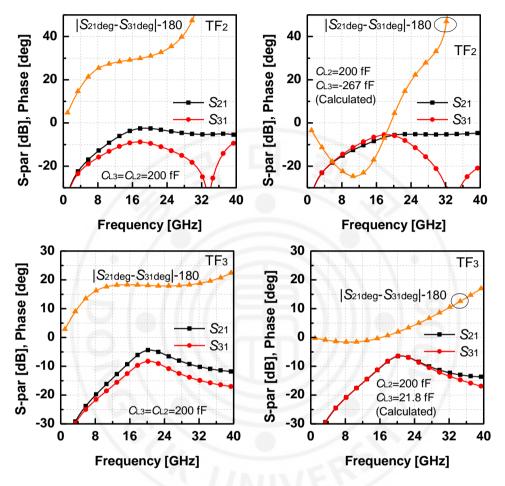

| Figure 5.5. Three port network balun with a current source and two load admittance 101                                                        |

| Figure 5.6. Extracted Y-parameters of TF1 (slightly unbalanced), TF2 (strongly                                                                |

| unbalanced), and TF3 (unbalanced)                                                                                                             |

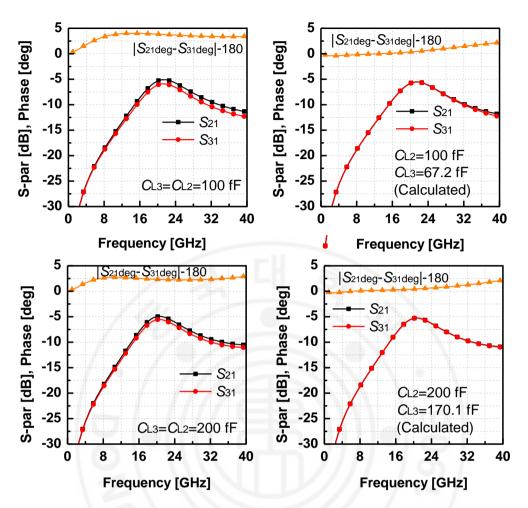

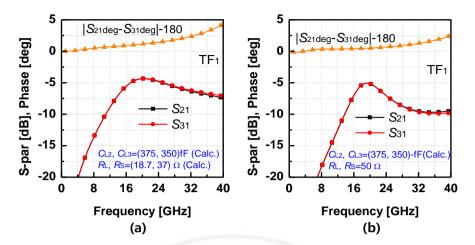

| Figure 5.7. Simulated $S_{21}$ and $S_{31}$ of TF1 at $C_{L2}$ =100-fF and 200-fF in the cases of $C_{L3}$ = $C_{L2}$                         |

| and calculated from (5.5)104                                                                                                                  |

| Figure 5.8. Simulated $S_{21}$ and $S_{31}$ of TF <sub>2</sub> and TF <sub>3</sub> at $C_{L2}$ =200-fF in the case of $C_{L3}$ = $C_{L2}$ and |

| the case $C_{L3}$ calculated from (5.5)                                                                                                       |

| Figure 5.9. Equivalent two-port network of a balun                                                                                            |

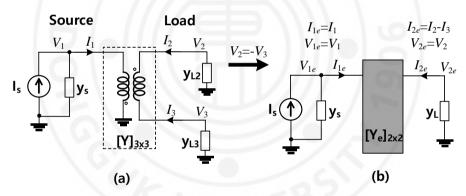

| Figure 5.10. Simulated $S_{21}$ and $S_{31}$ of TF1 at (a) the optimum load and source admittances                                            |

| and (b) with optimum load and source capacitances, and 50- $\Omega$ load and source                                                           |

| impedances                                                                                                                                    |

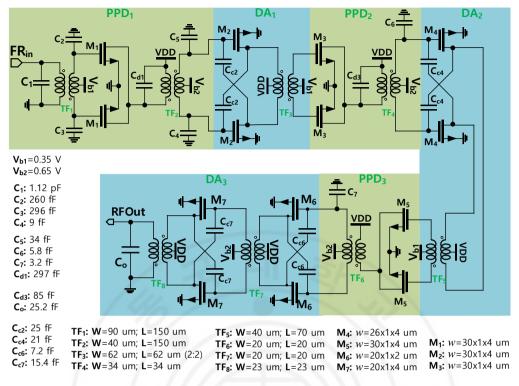

| Figure 5.11. Schematic of the x8 frequency multiplier                                                                                         |

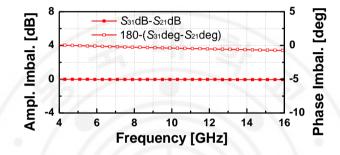

| Figure 5.12. Simulated amplitude and phase imbalances of the first balun (TF1)110                                                             |

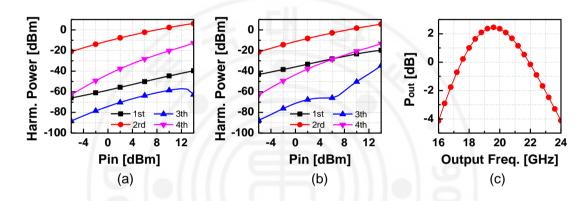

| Figure 5.13. The simulated power level of several harmonics of the first doubler at 10-GHz:                                                   |

| (a) the original design using the proposed method to balance the baluns; (b) using                                                            |

| differentially-connected capacitors for the baluns111                                                                                         |

| Figure 5.14. Simulated results of the second doubler: (a) Output power (Pout) versus input                                                    |

| power ( $P_{in}$ ) at output frequency $F_{out}$ =80-GHz; (b) $P_{out}$ versus $F_{out}$ at $P_{in}$ =7-dBm112                                |

| Figure 5.15. Simulated results of the third doubler: (a) Output power ( $P_{out}$ ) versus input                                              |

| power ( $P_{in}$ ) at output frequency $F_{out}$ =80-GHz; (b) $P_{out}$ versus $F_{out}$ at $P_{in}$ =7-dBm112                                |

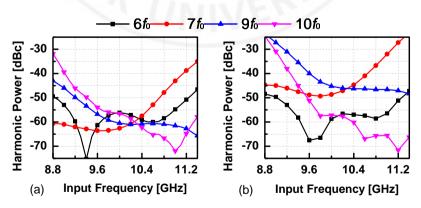

| Figure 5.16. Simulated harmonic power of the FM versus input frequency using proposed                                                         |

| balancing method (a), and conventional balun (b)                                                                                              |

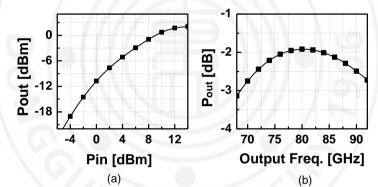

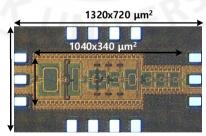

| Figure 5.17. Photograph of the x8 FM in 65-nm CMOS114                                                                                         |

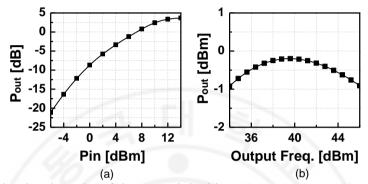

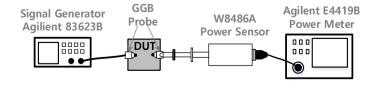

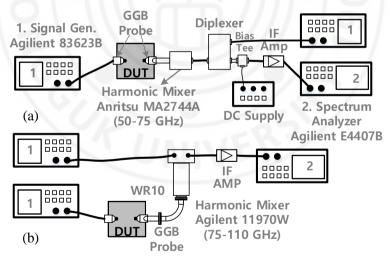

| Figure 5.18. Power measurement setup for the main harmonic                                                                                    |

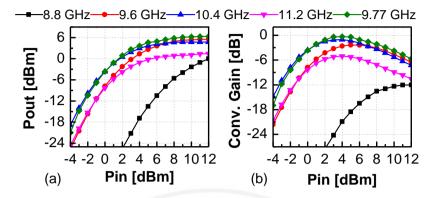

| Figure 5.19. (a) Measured output power (Pout) and (b) measured conversion gain of the $\times 8$                                              |

| FM versus input power (Pin)115                                                                                                                |

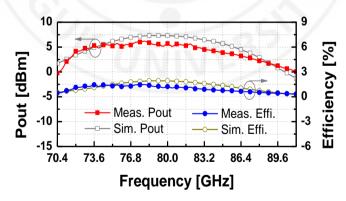

| Figure 5.20. Measured output power (Pout) and efficiency of the $\times 8$ FM versus output                                                   |

| frequency115                                                                                                                                  |

| Figure 5.21. Power measurement setup for the 6th, 7th, 9th, and 10th harmonics116                                                             |

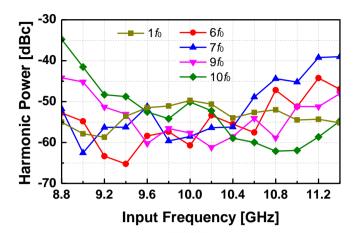

| Figure 5.22. Measured output power values at the 1st, 6th, 7th, 9th, and 10th harmonics.  | . 117 |

|-------------------------------------------------------------------------------------------|-------|

| Figure 6.1. An active two-port device with its source and load.                           | .120  |

| Figure 6.2. An active two-port device is embedded in an LLR network                       | .121  |

| Figure 6.3. Post-layout simulated power gains and stability factor of a 32 $\mu$ m common |       |

| source NMOS transistor in a 65 nm CMOS process.                                           | .122  |

| Figure 6.4. An LTI network is connected to a source $y_S$ and a load $y_L$                | .123  |

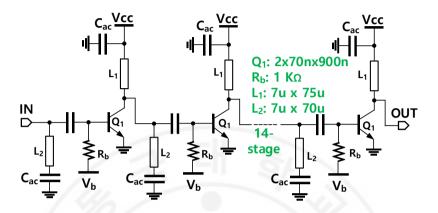

| Figure 6.5. Schematic of the 280-GHz amplifier on 130-nm SiGe.                            | .125  |

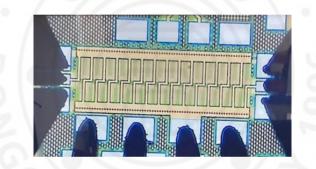

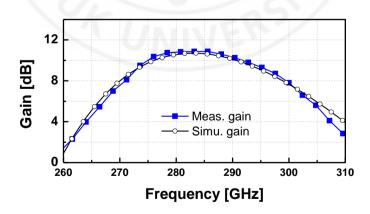

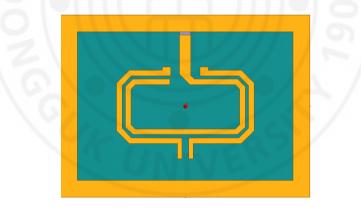

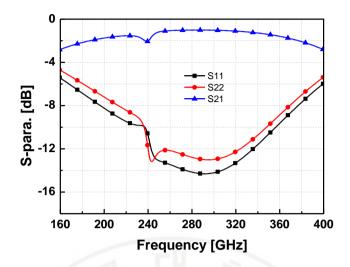

| Figure 6.6. A photograph of the 280-GHz amplifier.                                        | .125  |

| Figure 6.7. Simulated and measured gain of the 280-GHz amplifier                          | .125  |

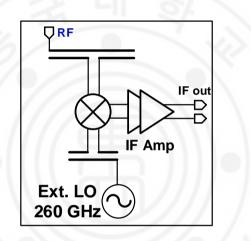

| Figure 6.8. Block diagram of the 280-GHz receiver.                                        | .126  |

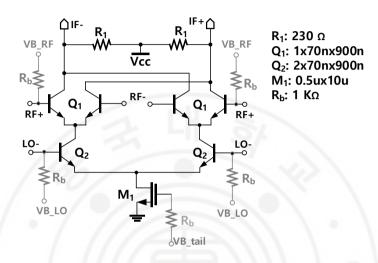

| Figure 6.9. Schematic of the mixer in the 280-GHz Rx.                                     | .127  |

| Figure 6.10. Simulated gain and NF of the mixer.                                          | .127  |

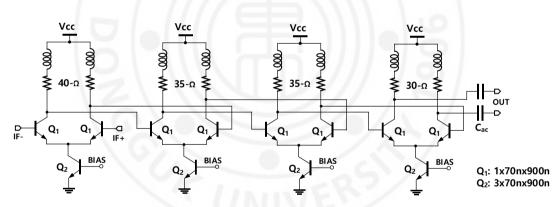

| Figure 6.10. Schematic of the IF amplifier in the 280-GHz receiver.                       | .128  |

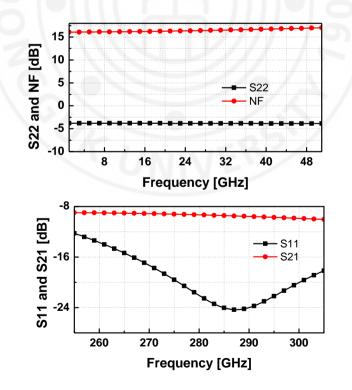

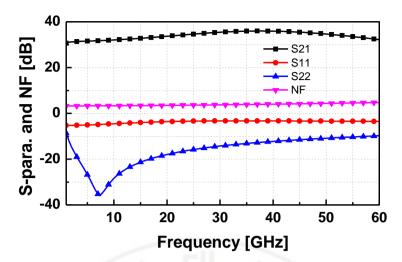

| Figure 6.11. Simulated S-parameters and NF of the IF amplifier                            | . 129 |

| Figure 6.12. HFSS implementation of the Marchand balun at RF input.                       |       |

| Figure 6.13. Simulated S-parameters of the RF balun                                       | .130  |

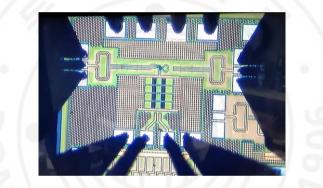

| Figure 6.14. A photograph of the measured 280-GHz receiver                                | .130  |

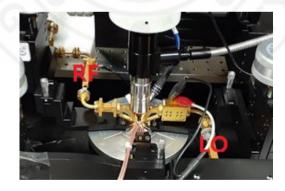

| Figure 6.15. Measurement setup for the gain of the mixer-first 280-GHz Rx                 | .130  |

| Figure 6.16. Measured and simulated gain of the 280-GHz Rx.                               | .131  |

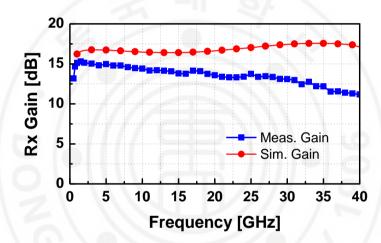

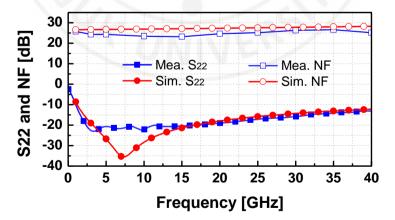

| Figure 6.17. Measured NF and S22 of the 280-GHz receiver.                                 | .131  |

|                                                                                           |       |

|                                                                                           |       |

| LIST OF TABLES                                                                            |       |

| Table 1.1 Channels is in a full frame to the share been state [1,5]                       | 2     |

| Table 1.1 Characteristics of different technology nodes [1.5]                     | . 2 |

|-----------------------------------------------------------------------------------|-----|

| Table 2.1. Comparison between TF-based pseudo differential amplifiers and         |     |

| Common source single-ended amplifiers                                             | 12  |

| Table 3.1. Characteristic parameters of the equivalent TF of the output PC at 10- |     |

| GHz                                                                               | 40  |

| Table 3.2. Summary of State-Of-Art Silicon-based PAs around X-band                | 45  |

| Table 3.3. Summary of the CMOS PAs around the X-band                              | 51  |

| Table 3.4 Summary of the CMOS PAs around X-band                                   | 54  |

| Table 4.1. Performance of the output transistor at different sizes                | 65  |

| Table 4.2. Summary of state-of-art mm-wave CMOS PAs around 77 GHz                 | 70  |

| Table 4.3. Transistor parameters of the 8-way PA                                  | 82  |

| Table 4.4. Extracted parameters of transformers and inductor of the 8-way PA      | 82  |

| Table 4.5. Summary of State-Of-The-Art CMOS PAs around W-Band                     | 85  |

| Table 4.6. Summary of the proposed PA with recent CMOS PAs in the W-band.         | 90  |

| Table 5.1. Efficiency and the imbalance level of the baluns at 20-GHz 10          | 00  |

| Table 5.2. Comparison of state-of-the-art FMs around W-band1                      | 17  |

### **ABBREVIATIONS**

| IC       | Integrated Circuit                      |

|----------|-----------------------------------------|

| RF       | Radio Frequency                         |

| RFIC     | Radio Frequency Integrated Circuit      |

| PA       | Power Amplifier                         |

| DA       | Driving Amplifier                       |

| HPA      | High Power Amplifier                    |

| TRx      | Transceiver                             |

| Tx       | Transmitter                             |

| Rx       | Receiver                                |

| LO       | Local Oscillator                        |

| IF       | Intermediate Frequency                  |

| FM       | Frequency Multiplier                    |

| HRR      | Harmonic Rejection Ratio                |

| CMOS     | Complementary Metal-Oxide-Semiconductor |

| BJT      | Bipolar-Junction-Transistor             |

| HEMT     | High Electron Mobility Transistor       |

| FET      | Field Effect Transistor                 |

| SOI      | Silicon-on-Insulator                    |

| AESA     | Active Electronically Scanned Array     |

| LNA      | Low Noise Amplifier                     |

| TRM      | Transmitter/Receiver module             |

| SPDT     | Single Pole Double Throw                |

| VCO      | Voltage Control Oscillator              |

| PLL      | Phase Locked Loop                       |

| ADC      | Analog to Digital Converter             |

| DAC      | Digital to Analog Converter             |

| FMCW     | Frequency-Modulated Continues-Wave      |

| TF       | Transformer                             |

| TF-based | Transformer-based                       |

| FoM      | Figure-of-Merit                         |

| CS       | Common Source                           |

| AC       | Alternating Current                     |

| DC       | Direct Current                          |

| СМ       | Common Mode                             |

| BEOL     | Back End of Line                        |

| SRF      | Self-Resonant Frequency                 |

| EM       | Electromagnetic                         |

| HB       | Harmonic Balance                        |

| CAD      | Computer-Aided Design                   |

| RHP      | Right-Half Plane                        |

| CCT      | Current Combining Technique             |

| VCT      | Voltage Combining Technique             |

| CPC      | Current Power Combiner                  |

| VPC      | Voltage Power Combiner                  |

|          | -                                       |

| PCV Power Combiner on Voltage domain<br>PC Power Combiner |   |

|-----------------------------------------------------------|---|

|                                                           |   |

| PS Power Splitter                                         |   |

| DAT Distributed Active Transformer                        |   |

| UTM Ultra-thick Metal                                     |   |

| PAE Power Added Efficiency                                |   |

| OP1dB Output 1-dB gain compression point                  |   |

| Psat Saturated Power                                      |   |

| OIP3 Output Third Order Intercept Point                   |   |

| E2PN Equivalent Two Port Network                          |   |

| ESD Electrostatic Discharge                               |   |

| TMN Transformer-based Matching Network                    | ĸ |

| IL Insertion Loss                                         |   |

| PN Phase Noise                                            |   |

| PPD Push-push Doubler                                     |   |

| A2P Active two-port device                                |   |

| NF Noise Figure                                           |   |

#### **I. Introduction**

#### 1.1. Motivation

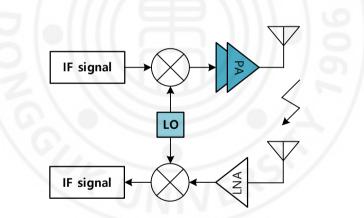

Transceiver, which has more than a century of development, still witnesses constant innovation to adapt to the rapid change of advanced integrated circuitry (IC) technologies and revenue itself with new physical characteristics found at higher frequencies. Specifically, recent advancements in IC technologies with increasing cut-off frequency allow transceiver systems to work at higher frequencies with the benefits of surging in operation bandwidth, ushering in the era of data explosion [1.1]. Ultra-low-power, low-cost transceivers also are becoming spot-light that adapt to connecting an increasing number of mobility devices in the "internet-of-thing" era, aiming to implement smarter systems [1.2]. Another trend of transceiver technology is the movement toward higher frequency with promising applications found at sub-terahertz such as secure scanning, and imaging in medicine [1.3]. The architecture of a transceiver might be varied for different applications and operating frequencies. However, most of them can be simplified with a radio-frequency (RF) interface shown in Figure 2.1.

Figure 1.1. Typical simplified RF interface of a transceiver system.

In this thesis, we mainly focus on investigating and enhancing the performance of the power amplifier (PA) and the local oscillator in the transceiver architecture. Because power amplifiers are the most power-hunger block in a transceiver system, their efficiency dominates the energy efficiency of the TRx. The power efficiency is an especially critical factor for mobile devices to extend their battery usage time, which is one of the most important commercial user-performance. In addition, power amplifiers are the block working at the largest signal. Its linearity directly affects the spectrum efficiency of a TRx

system as surveyed in [1.4]. Also working in the large signal mode, the LO was required to provide clean and stable oscillation for the mixer to perform the conversion function between intermediate frequency (IF) and RF signals. Specifically, these criteria are quantified by the harmonic rejection ratio (HRR) for a frequency multiplier (FM), the flatness of output power over the sweeping frequency, and the phase noise of the input signal for the FM, which finally turns into the phase noise at the output with an increase of the multiplication factor.

The trends toward high-data-rate, ubiquitous wireless communication have opened up challenges and also opportunities for RF designers to implement high-efficiency power amplifiers on the advanced IC technologies. The recent development on physics-level platforms allows IC processes to achieve increasing cut-off frequencies ( $f_i$ ), but with lower supported supply voltage, and break down voltages as well. Table 1.1 shows the reducing trend of nominal supplying voltage for different technology nodes over the years. The reduced switching time benefits digital designs with smaller, faster, and lower-power designs. It also allows the RF interface to operate at a higher frequency. However, the less gain of the active device and the more severe loss of the passive components at high frequencies are hindrance factors to arrive at ideal high-efficiency, high-power, wide bandwidth, and high linearity PA designs. Similarly, there are also technical trade-offs between high-power, wide bandwidth, and low phase noise performances for LO implementation. Depending on the specification of the TRx system, a designer could determine which performances are of higher priority for a specific design.

| Production year | Technology node | Technology type | VDD (V) |

|-----------------|-----------------|-----------------|---------|

| 1999            | 180             | Bulk            | 1.8     |

| 2001            | 130             | Bulk            | 1.2     |

| 2004            | 90              | Bulk            | 1.1     |

| 2007            | 65              | Bulk            | 1.1     |

| 2008            | 45              | High-k          | 1.1     |

| 2010            | 32              | High-k          | 0.97    |

| 2012            | 20              | Multi-Gate      | 0.9     |

| 2013            | 16              | Multi-Gate      | 0.86    |

| 2013            | 14              | Multi-Gate      | 0.86    |

| 2015            | 10              | Multi-Gate      | 0.83    |

| 2017            | 7               | Multi-Gate      | 0.8     |

Table 1.1 Characteristics of different technology nodes [1.5]

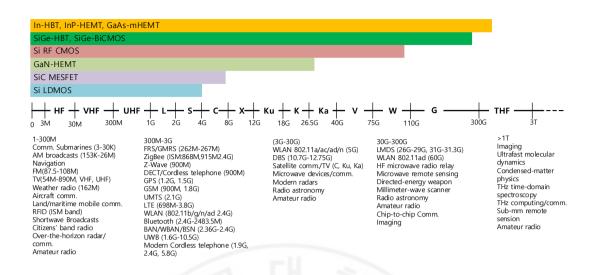

Figure 1.2. Applications of power amplifiers over frequency bands [1.4].

The graph of the application of power amplifiers distributed over frequency is illustrated in Figure 1.2 [1.4]. It also shows the typical technologies used at different frequencies. It is noticed that compared to the raw figure in [1.4], we have updated the frequency range of GaN-HEMT, Si RF-CMOS, and SiGe-BiCMOS based on our experiences with these technologies. It can be seen that power amplifiers (or transceivers in more general) have been found in various applications both civil and military. In this thesis, we have developed PAs, LOs and down-converter in X-band (8-12G), E-band (71-86G), and sub-terahertz band (280-GHz). Various applications can be found in these bands as listed in Figure 1.2. Herein, we briefly describe some applications at these bands in the followed sections including Active Electronically Scanned Array (AESA) radar at X-band, automotive radar at 77-GHz, wireless point-to-point communication in E-band, and wireless communication at the subterahertz band.

#### **1.2.** Applications

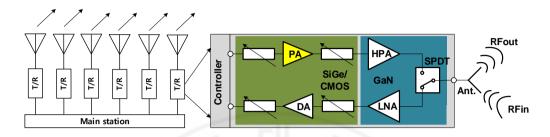

#### 1.2.1. Active Electronically Scanned Array (AESA) in X-band

The basic concept of an AESA system is based on the fundamental working principle of a normal radar in which a transmitter (Tx) will send a short signal pulse through the antenna. Right after that, the antenna is disconnected from Tx to connect to an Rx by using a switch. By measuring the delay time of the returned signal, we can determine the distance to the reflecting object. In AESA systems, the signal from a single source (called the main station) is connected to an array of TRx modules that can control the phase of the signal on each path separately (Figure 1.3). In this way, the beam can be steered quickly, thus AESA radar can scan the space much faster than using mechanical systems. Moreover, since subbeams can be produced at different frequencies, the AESA radar can track a large number of targets simultaneously.

Figure 1.3. Simplified block diagram of AESA system.

Figure 1.3 also illustrates a block diagram of recent T/R modules (TRM) used in AESA systems. Typically, the TRMs are consist of a front-end module that is connected to the antenna and a back-end module that is connected to the main station. The front-end block is typically implemented on GaN technologies. Due to the very high  $g_m$  of these technologies, we could design very high-power PAs (in the range of 46 dBm [1.6]). The LNA and the switch using GaN also can achieve very good performance. One disadvantage of GaN technologies has lied in their low integration level. Therefore, the back-end module with phase controllability is typically designed in SiGe or CMOS processes. To compensate for the loss of the passive phase delay blocks, it still requires a driving amplifier and power amplifiers in the back-end module, which is normally required to provide up to >20-dBm output power at the transmitting path to sufficiently drive the front-end HPA.

#### 1.2.2 Automotive radar at 77-GHz

W-band is suitable for radar sensors in traffic vehicles because by using such a small wavelength, the radar could detect efficient small objects the size of a human, small cars, or traffic poles on the street. The high-frequency usage also makes the radar system faster in measuring high moving objects. In addition, W-band has stronger penetration property compared to a lower frequency, which makes it more reliable to be used in extreme environments such as bad weather conditions [1.7-1.8]. Due to these reasons, it is recommended by ITU for the automotive radar application (76-81 GHz) [1.9]. In [1.9], detailed specifications for automotive radars at different positions on a car are recommended.

Notably, the recommended output power of 10-dBm for the power amplifier is quite relaxed for RF CMOS processes which can cover the typical detection range of ~250m.

Figure 1.4. Simplified block diagram and working principle of an FMCW radar.

Automotive radars work based on the principle of the well-known frequency-modulated continues-wave (FMCW) radar which radiates continuous transmission power with the changed radiation frequency to detect the distance and velocity of the measured object. A simplified block diagram of a typical FMCW radar is shown in Figure 1.4. A detailed description of an FMCW radar can be found in [1.10]. An FMCW radar consists of a frequency synthesizer that can alter its output frequency signal based on the controlled signal from the processor. A transmitter including a PA and an antenna will radiate the frequency-modulated signal. A receiver using the same oscillation from the frequency synthesizer is used to detect the reflected signal. To detect the distance of the measured object, the FMCW radar measures the time delay of the reflected signal from the object to calculate the distance which is finally simplified to be the formula shown in Figure 4.1. Meanwhile, the velocity is measured based on the Doppler effects. On the basic, the frequency of the reflected signal is shifted up or down based on the relative velocity of the object with respect to the radar. By measuring the amount of the frequency shift, we could calculate the velocity of the

measured object. The equation to calculate the relative velocity of the object is presented in Figure 1.4 as well.

1.2.3 Point-to-point wireless communication in E-band for 5G backhaul

Figure 1.5. The logical architecture of the 5G backhaul network [1.11].

We are living in an era of data explosion generated by a huge number of connected devices which target building up a smarter life. This naturally leads to the born of the next generation networks (5G). The logical architecture of the 5G network is shown in Figure 1.5 [1.11]. A network's backhaul is the connection between the core network and its subnetworks. Through backhaul, the mobile network is connected to the wired network in 5G. Hence, 5G backhaul refers to signals between 5G cores and remote sites or networks. From the core network, 5G backhaul will need to support hundreds of gigabits of traffic per second. It is critical to the success of 5G to build out the backhaul infrastructure to allow for high speeds, large capacities, and wide bandwidths for multiple connected devices.

In the current infrastructure, fibers and wires are typically buried underground, or wireless antennas are attached to street lamps. Backhaul for generations before 5G will not be able to cope with the high density, low latency, and ultra-data-rate demands of 5G. A new backhaul infrastructure is therefore required. Backhaul over fiber generally proves to be difficult to deploy and expensive to install. Furthermore, laying enough fiber to connect everything to the core can take months. By eliminating wires or cables for wireless data transport, wireless backhaul facilitates easier installation. Backhaul via wireless (microwave and millimeter-wave) appears to be more readily available and easier to deploy. E-band (71-

86G) transceivers are a promising solution for 5G backhaul wireless links due to their supportability of wideband implementation (~10G). Moreover, transceivers at E-band could benefit from the reduced-cost and high-integrated level when Eband PAs are possible to be implemented in the CMOS process with sufficient output power of ~15 dBm to cover the typical required communication range of ~1-2 Km in urban areas [1.12-1.13].

1.2.4 Wireless communication at the sub-terahertz band

Figure 1.6. Target applications of wireless communication at sub-THz bands [1.17].

As shown in Figure 1.2, sub-terahertz (sub-THz) and beyond could be applicable in sensing and short-range wireless communication. Operating at shorter wavelengths could help an imaging system achieve better resolutions. The special absorption spectral of some materials and products to the sub-THz and THz bands also make spectroscopies at these bands to be employed in agriculture and food products, detection of concealed or dangerous objects, cancer scanning, etc [1.14-1.16]. Particularly, by shifting to sub-THz frequencies, wireless systems could potentially achieve a much broader bandwidth which is expected up to hundreds of Gbps.

The development of a 5G mobile network at microwave and mm-wave is currently almost complete. Venders are testing their system at the user level before it can be deployed on a large scale. Recent demonstrations of sub-terahertz transceivers have opened up a vision for a 6G network that could achieve an explosion in data rate, and time delay compared to a 5G network. The first standardization efforts for sub-terahertz band wireless connection could be found in [1.17]. Such short-range wireless links could be used in data

centers, device-to-device connections, front-haul and back-haul mobile networks, or Kiosk downloading as shown in Figure 1.6.

#### 1.3. Thesis organization

In this thesis, we investigate design techniques to attain high-performance and robust push-pull power amplifiers. Based on that, we demonstrate power amplifier designs at Xband and E-band with the oriented performance of high-power, high-efficiency, and area minimization. An E-band frequency multiplier is also presented using transformer-based push-push doubler for a highly-clean local oscillation source. In sub-terahertz band, we present an implemented amplifier and a wideband receiver at 280-GHz in 130-nm SiGe.

Chapter 2 presents an analysis of the impedance matching network using transformers that are verified by measurement data for the transformer model as well as the synthesized matching formula. Besides the importance of impedance matching in improving the efficiency of the TF-based PAs, their robust operation against possible common mode oscillations is investigated, resulting in several useful guidelines to suppress instabilities.

Chapter 3 demonstrates three X-band power amplifiers with enhancement on either output power, operation bandwidth, or efficiency. First, we present a CMOS PA design on 65-nm CMOS utilizing a 6-way TF-based power combiner/splitter to achieve a well-balanced performance with an outstanding figure-of-merit (FoM) of 85-dB compared to other CMOS PAs. The second X-band PA on 65-nm CMOS was designed aiming at wideband operation and high output power. The third PA design is the demonstration of a proposed structure, called a "single-pull" amplifier which could be suitable for low-cost implementation.

In chapter 4, three PAs at E-band using push-pull amplifying structure are presented. First, we present a compact, high efficient PA design at 77-GHz on 65-nm CMOS for automotive radar application. Secondly, we demonstrate the feasibility of using a high-way voltage combination to enhance output power at the E-band with an 8-way PA design fabricated on 65-nm CMOS which could achieve ~19 dBm of measured output power. The final content of this chapter describes an mm-wave push-pull power amplifier using a neutralization inductive feedback network which is proposed to obtain good trade-offs between PA's performance merits.

In chapter 5, an eight-time frequency multiplier (FM) design at E-band was described. The FM used three stages of push-push frequency doublers that applied a new balancing technique for the TF-baluns to improve the harmonic rejection ratio (HRR). Experimental results are presented in comparison with other reported frequency multipliers recently.

In chapter 6, we present an amplifier and a receiver front-end at 280-GHz on 130-nm SiGe technology. The measured results are shown in comparison to the simulation values.

#### 1.4. Reference

- [1.1] A. Gupta and R. K. Jha, "A Survey of 5G Network: Architecture and Emerging Technologies," in *IEEE Access*, vol. 3, pp. 1206-1232, 2015.

- [1.2] J. Blanckenstein, J. Klaue, and H. Karl, "A Survey of Low-Power Transceivers and Their Applications," in *IEEE Circuits and Systems Magazine*, vol. 15, no. 3, pp. 6-17, thirdquarter 2015.

- [1.3] X. Lu, S. Venkatesh, and H. Saeidi, "A review on applications of integrated terahertz systems," in *China Communications*, vol. 18, no. 5, pp. 175-201, May 2021.

- [1.4] J. Joung, C. K. Ho, K. Adachi, and S. Sun, "A Survey on Power-Amplifier-Centric Techniques for Spectrum- and Energy-Efficient Wireless Communications," in *IEEE Communications Surveys & Tutorials*, vol. 17, no. 1, pp. 315-333, First quarter 2015.

- [1.5] Aaron Stillmaker, Bevan Baasa, "Scaling equations for the accurate prediction of CMOS device performance from 180 nm to 7 nm," Integration, the VLSI journal, vol 58, pp. 74-81, June 2017.

- [1.6] M. Oppermann and R. Rieger, "Multifunctional MMICs Key Enabler for Future AESA Panel Arrays," 2018 IMAPS Nordic Conference on Microelectronics Packaging (NordPac), 2018, pp. 77-80.

- [1.7] S. M. Patole, M. Torlak, D. Wang, and M. Ali, "Automotive radars: A review of signal processing techniques," IEEE Signal Process. Mag., vol. 34, no. 2, pp. 22–35, Mar. 2017.

- [1.8] H. Jia, L. Kuang, W. Zhu, Z. Wang, F. Ma, Z. Wang, and B. Chi, "A 77 GHz frequency doubling two-path phased-array FMCW transceiver for automotive radar," *IEEE J. Solid-State Circuits*, vol. 51, no. 10, pp. 2299–2311, Oct. 2016.

- [1.9] "Systems characteristics of automotive radars operating in the frequency band 76-81 GHz for intelligent transport systems applications," *Recommendation ITU-R* M.2057-0 (02/2014).

- [1.10] T. Ma et al., "A CMOS 76–81-GHz 2-TX 3-RX FMCW Radar Transceiver Based on Mixed-Mode PLL Chirp Generator," in *IEEE Journal of Solid-State Circuits*, vol. 55, no. 2, pp. 233-248, Feb. 2020.

- [1.11] X. Ge, H. Cheng, M. Guizani and T. Han, "5G wireless backhaul networks: challenges and research advances," in *IEEE Network*, vol. 28, no. 6, pp. 6-11, Nov.-Dec. 2014.

- [1.12] Al-Saman, A.; Mohamed, M.; Cheffena, M.; H. Azmi, M.; A. Rahman, T. Performance of Full-Duplex Wireless Back-Haul Link under Rain Effects Using E-Band 73 GHz and 83 GHz in Tropical Area. *Appl. Sci.* 2020, *10*, 6138.

- [1.13] V. -S. Trinh and J. -D. Park, "An 85-GHz Power Amplifier Utilizing a Transformer-Based Power Combiner Operating Beyond the Self-Resonance Frequency," in *IEEE Journal of Solid-State Circuits*, vol. 57, no. 3, pp. 882-891, March 2022.

- [1.14] V. P. Wallace et al., "Terahertz pulsed imaging of basal cell carcinoma ex vivo and in vivo," British Journal of Dermatology, Vol. 151, pp. 424-432, 2004.

- [1.15] E Pickwell and V.P. Wallace. "Biomedical applications of terahertz technology," *Journal of Physics D: Applied Physics*, Vol 39, pp. R301- R310, 2006.

- [1.16] Ashish Y. Pawar, Deepak D. Sonawane, Kiran B. Erande, Deelip V. Derle, "Terahertz technology and its applications" Drug Invention Today, Volume 5, Issue 2, June 2013, Pages 157-163.

- [1.17] V. Petrov, T. Kurner and I. Hosako, "IEEE 802.15.3d: First Standardization Efforts for Sub-Terahertz Band Communications toward 6G," in *IEEE Communications Magazine*, vol. 58, no. 11, pp. 28-33, November 2020.

#### II. Impedance matching and stability analysis for TF-based PA

#### 2.1 Introduction

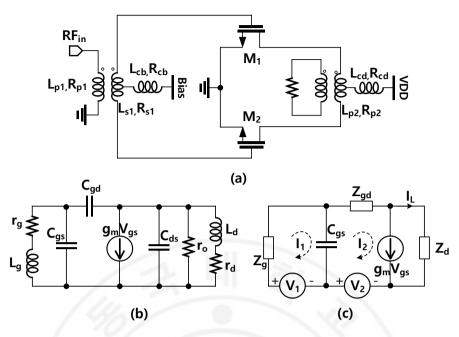

Today, radio frequency integrated circuits (RFICs) include transformers (TFs) that are widely used for various purposes, such as impedance matching, impedance transformation, and signal conversions between single-ended and differential at various frequencies. If they are used to transform impedance or balance signals, transformers should ensure maximum power transfer to the load. Ideally, the input and output of a TF should be conjugately matched to its source and load impedances. Designing an efficient transformer network has been considered an essential task which has been implemented with several iterations with the aid of computer simulation since the input and output impedance are simultaneously affected by each other owing to the reciprocal nature of a passive network.

In this chapter, we investigate on a TF-based impedance matching network utilizing a simplified two magnetically coupled coils model connected to a source and a load. We investigate the matching requirement at two ports depending on the transformer parameters as well as the source or the load impedance connected to its counterpart port, and a detailed analysis of various impedance conditions for the transformer network is presented. Based on this work, analytic formulae for constructing a transformer network with a resistive load having a parallel tuning capacitor are provided. We also examined on-chip transformers implemented in 0.18 µm CMOS technology to assess the validity of the proposed work.

The prevalence of a differential amplifier in common-source (CS) configurations is owing to its distinct benefits. Table 2.1 presents a comparison between the TF-based pseudo differential amplifiers (also called push-pull amplifiers) and CS single-ended amplifiers. The differential pair combines the power of two active devices to a load, thereby helping to release the voltage stress on the device's drains. It is a well-balanced structure when implying the natural two-pole property of an AC signal which maximizes the combining efficiency, mitigates CM interference and noise, and facilitates circuit layout owing to the symmetry structure. Therefore, the differential pair is commonly used as the unit cell when output power combining is exploited for a higher output power. However, it is well known that a CM oscillation can be triggered in a differential amplifier at a high frequency if the losses in the path of any feedback loop are not significant enough to guarantee robust stability. This chapter also deals with issue of detecting instability and stabilizing the network in the early stages of the design.

Table 2.1. Comparison between TF-based pseudo differential amplifiers and common source single-ended amplifiers

|                          | TF-based pseudo differential<br>amplifiers                                                                                        | Common source single-ended amplifier                                                                                                        |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Output power             | $Z_{out}=Z_{device}/2 \Rightarrow$ could support<br>four time output power larger<br>than CS amplifier with the same<br>$Z_{out}$ | $Z_{out} = Z_{device} =>$ support no power combination                                                                                      |

| Neutralization           | Can be neutralized by cross-<br>connected capacitors between<br>the gates and drains =><br>broadband and easy in layout           | Typically uses de-Qing resistors in<br>the gate or use RC-feedback<br>between drain to gate => trade-offs<br>between stabilization and loss |

| Layout                   | More compact with TFs                                                                                                             | Less compact (LC or Tline matching)                                                                                                         |

| Instability<br>issue     | Suffer from common-mode<br>instability => can be easily<br>suppressed by neutralizing<br>capacitor and de-Qing feedback<br>paths  | Suffer from odd-mode instability<br>when using common-mode power<br>combination => can be suppress<br>with de-Qing odd-mode resistors       |

| Efficiency               | Get worse at high frequency due<br>to the loss of TFs                                                                             | Achieve better efficiency at high<br>frequency with TLine-based<br>matching networks                                                        |

| At F>f <sub>max</sub> /2 | Loss of TFs are significant<br>compare to gain of transistor<br>=> not suitable to be used                                        | More suitable because LC or Tline<br>matching offer less loss compared<br>to TF-based matching                                              |

#### 2.2 Impedance matching for transformers

The magnetic coupling between two or more conductors in a passive transformer allows an input signal or input power to be transmitted to the load. An example of an implemented on-chip 2:1 transformer on silicon is given in Figure 2.1. The series resistance of each winding is quite significant when winding TFs are fabricated on a silicon substrate. This is because the windings are fabricated on relatively thin metal layers within BEOL dielectric layers, and the skin effect plays a role in the series resistance. Transformers model typically consists of two magnetically coupled coils, as shown in Figure. 2.2. This simplified transformer model relies on five parameters: series resistance ( $R_1$  and  $R_2$ ), inductance ( $L_1$ and  $L_2$ ), and coupling coefficient, which indicates the amount of magnetic coupling between the two windings [2.1].

Figure 2.1. On-chip 2:1 TF structure for 3D electromagnetic simulation: (a) the front face, (b) a 3D view in HFSS, and (c) a side view of the layer stacks.

Figure 2.2. Magnetically coupled TF model with load and source.

It is defined that  $n=L_1/L_2$  is the turns ratio between the two wounds. Since the complexity of the model and analysis was considerably increased as a result of parasitic coupling capacitance, the effect was marginal at the frequency of interest (below SRF) when it was considered in this section. Following the basic low-frequency model, transformers are widely characterized as core circuits in many studies since the physical size of transformers tends to be considerably smaller than the guided wavelength at operating frequencies [2.1]. Due to this, it is possible to interpret dominant physical phenomena occurring in TFs at operating frequencies well below the transformer's SRF with inductors and magnetic couplings between them. The conjugate matching on both sides of the TF is either possible if the transformer is ideal ( $R_1=R_2=0$ ) or if  $Z_s$  and  $Z_L$  satisfy the conditions given by [2.2]

$$X_L = -\omega L_2, X_S = -\omega L_1$$

(2.1.1)

$$\left[R_{L} = R_{2}\sqrt{1 + k^{2}Q_{1}Q_{2}}, R_{S} = R_{1}\sqrt{1 + k^{2}Q_{1}Q_{2}}\right]$$

(2.1.2)

The maximum available gain of a transformer in the case of simultaneous conjugate matching conditions on both sides of the transformer given by [2.2] as

$$G_{T_{\text{max}}} = 1 - 2 \frac{\sqrt{k^2 Q_1 Q_2 + 1} - 1}{k^2 Q_1 Q_2}$$

(2.2)

Even (2.1) provides the general solution for the load and the source of a transformer network, the more frequently used matching style for a transformer is to use parallel capacitors at their input and output as shown in Figure 2.3. This structure offers great convenience in layout, and any parasitic capacitances of the active devices the transformer is connected to are also easily aborted by the parallel matching capacitor. The optimum values of the resistance and capacitance in the parallel configuration were reported in [2.2] to be

$$\begin{cases} R_{Lopt} = R_2 \sqrt{1 + k^2 Q_1 Q_2} \left( 1 + \frac{Q_2^2}{1 + k^2 Q_1 Q_2} \right) \\ C_{topt} = \frac{L_2}{R_2^2 (1 + Q_2^2 + k^2 Q_1 Q_2)} \end{cases}$$

(2.3)

To verify the transformer model and the EM simulation in HFSS, we implemented and measured a single transformer in a 0.18  $\mu$ m CMOS process. Moreover, to demonstrate the validity of the parallel matching equation of (2.3), we fabricated a bunch of transformer networks in which only the parallel matching capacitor was varied. Photographs of the stand-alone transformer and its porotypes with different parallel matching capacitors fabricated on a 0.18  $\mu$ m CMOS process are shown in Figure 2.4

Figure 2.3. The TF impedance matching network using a parallel capacitor.

Figure 2.4. Photographs of the on-chip TFs in 0.18  $\mu$ m CMOS: (a) the standalone 2:1 transformer, and (b) transformers with parallel tuning capacitors.

From the measured s-parameters of the standalone 2:1 transformer, its parameters including resistances and inductances of the two coils and the coupling factor were extracted, which are shown in Figure 2.5 in comparison with its simulation results from the 3D model in HFSS. The extracted maximum available gain of the fabricated transformer was also shown in Figure 2.6 beside its counterpart on simulation. Overall, the simulation results corresponded well with the measured results. It can be seen that lower measured quality factors were recorded, which would cause by several lossy factors which were not modeled in HFSS such as the roughness of the metal coils. Moreover, in the real case, loss tangents of dielectric materials can vary depending on the frequency, while in HFSS they are regarded as constants.

Figure 2.5. Effective parameters of the on-chip 2:1 TF on simulation (dashed line) and measurement (solid line).

Figure 2.6.  $G_{Tmax}$  versus frequency of the on-chip 2:1 TF.

The matching equation of (2.3) was validated by measuring several fabricated transformers with different parallel capacitors at the load. We de-embedded the S-parameters from the RF pads and transmission lines. Afterward, power efficiencies for specific loads of 50  $\Omega$ and 100  $\Omega$  were obtained as shown in Figure 2.7. The data showed that the optimum  $C_t$  for both loads differed by about 20 fF (nearly 7%) from the simulation. This shift can be explained by the difference in  $C_{topt}$  between the model and the fabricated transformer based on the extracted parameters. This could also be a result of process variations resulting in a different nominal capacitance than what was specified by the manufacturer. The similarity between the measured results and the calculated data from the formula (2.3) proves the helpfulness of the analytical equation.

Figure 2.7. Power efficiency versus parallel tuning capacitances for the on-chip 2:1 TF at 10 GHz.

#### 2.3 Common-mode instability in push-push power amplifiers

#### 2.3.1 Introduction

The differential pairs of common-source (CS) transistors are commonly used as unit cells when output power combining is exploited for a higher output power [2.3]-[2.4]. During the early stages of the design process, it is crucial to detect instability and stabilize the network. Small-signal analysis has proven to be highly effective in identifying the major sources of instability in circuits with only a minimal computing effort required [2.5]-[2.6]. Despite this, there are still unstable points visible only at specific levels of RF input, and a small-signal analysis cannot detect them [2.7]. A transient simulation is an effective way to examine the unwanted behaviors of a circuit in the large-signal regime, but the computational resource requirements are high for complex designs [2.8]. To determine the stability of the circuit, designers should excite the circuit, such as by a step function in the supply and bias nodes. Harmonic balance simulations have also proven a promising way to detect instability, although the conventional HB simulator commonly found in CAD

programs has difficulty seeing it [2.7]. With additional applied methods, it can detect instabilities efficiently by using HB simulation [2.9], [2.10].

CAD tools can detect instability in a design. Still, it is quite a complex task since designers need to figure out the root cause of the instability to fix the design efficiently and achieve a good balance between stability and other performances. Manual analyses are important to thoroughly understand a specific circuit structure. The works in [2.11]–[2.12] had introduced some fundamental analysis on the stabilization of some circuit structures. One of the structures taken considerable interest from researchers in stability analysis is multi-branch paralleled PA because it uses power dividers and combiners between PA stages, which makes it prone to odd-mode instability. This issue has been investigated carefully both in the small-signal and large-signal domains in [2.5], [2.6], [2.10]. In [2.13], the authors have shown that a bypass capacitor connected to a non-ideal ground could lead to instability in push-pull amplifiers. In [2.14], we show that a differential amplifier can suffer from CM instability because of the gate inductance from the biasing line and the parasitic series coupling capacitance between the two coils of the input transformer.

#### 2.3.2 Oscillation mechanism in differential amplifiers

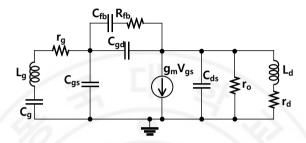

A pseudo-differential pair and a push-pull amplifier are widely used differential pair types in the microwave, with the output configuration demonstrated in Figure 2.8(a), and Figure 2.8(b), respectively. As the primary loss mechanism of CM signals, the inductive coils have relatively small parasitic series resistances, which makes the structure susceptible to instability. The combined effect of  $C_{gd}$  and the source's input impedance results in a positive feedback loop for the amplifier, leading to oscillations when a triggering signal is applied. Figure 2.8(c) shows a transient simulation of a differential push-pull PA implemented using 180-nm 1P6M CMOS technology. The amplifier oscillates when the supply voltage is turned on without an input signal, based on the simulation.

Figure 2.8. Instability in differential amplifiers (a) A pseudo-differential amplifier, (b) a push-pull amplifier, and (c) the simulated oscillation of the drain voltage of a transistor in a push-pull structure after turning on the supply voltage when there is no input signal.